TORONTO—One area where SRAM is seeing some continued stickiness is the growing automotive segment,

as vehicles continue to get smarter and provider more digital

information, whether it's to help the driver or entertain the

passengers.

The segment also includes autonomous vehicles, something Renesas

Electronics Corp. has in mind for its new two-port on-chip SRAM for use

in SoCs for in-vehicle infotainment systems. The new on-chip SRAM will

be used as video processing buffer memory in high-performance SoCs that

will play an important role in making the autonomous-driving vehicles of

the future safer and more reliable.In a telephone interview from Tokyo with EE Times, Koji Nii, chief professional for the Design Platform Business Department within Renesas' 1st Solution Business Unit, said the autonomous vehicle market is fast approaching on the horizon in Japan, as the country has committed to making it possible for highways to accommodate self-driving cars by 2019, followed by downtown city cores in 2022.

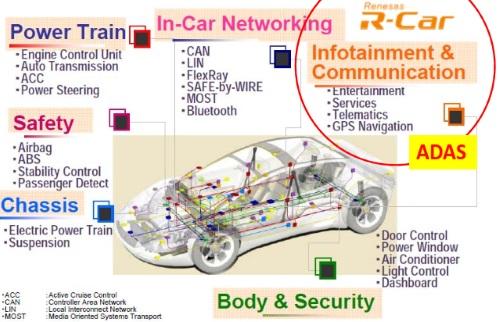

Already, advanced driver assistance systems (ADAS) such as automatic braking employing radar or other sensors have become widespread, as well as technology uses video data from vehicle cameras to recognize the peripheral environment and the driver in order to provide accurate information to the driver, said Nii. While Renesas supports a number of electronic systems within vehicles, encompassing MCU and SoC offerings for power train, chassis, in-car networking, safety and security applications, the new SRAM is aimed the infotainment and communication systems of the car, where fast, real-time processing is particularly important, including video.

A large amount of SRAM configured as high-performance internal buffer memory is essential for fast and accurate processing of video data. In addition to increasing the operation speed of the SRAM, said Nii, it's also critical to enable multi-port operation allowing simultaneous read and write accesses, which fetch video processing data for operations and store the data after operations finish.

Renesas has fabricated SRAM prototypes using a 16nm process that achieved a fast read access time of 313 picoseconds at the low voltage of 0.8 V. Nii said ingle-port SRAM cells are used to implement two-port SRAM functionality that allows independent read and write operations, making it possible to achieve fast read access alongside power efficiency and compact chip size.

Renesas

supports a number of electronic systems within vehicles, but its new

SRAM is aimed the infotainment and communication systems that require

fast, real-time processing.

The latest SRAM incorporates a double-pumping circuit technology using single-port SRAM cells, said Nii, which is what allows independent read and write operations, more compact memory area on the chip while maintaining fast read access, and reduced power consumption. Related to the latter is the development of a low-power circuit using a FinFET structure that effectively reduces leakage power to approximately one-half the previous level during the standby mode.

Switching from the planar transistor structure used with the earlier 28nm process to a 16nm FinFET structure provides improved transistor on-off characteristics while also changing the leakage current thermal characteristics and the voltage dependency. With the 28nm process, it was possible to reduce leakage current by lowering the voltage, but FinFET is less voltage-dependent, lowering the voltage did not decrease the leakage as much as anticipated. Instead, Renesas developed a low-leakage circuitry that applies bias to the source line potential of the new SRAM cells that reduces leakage while being relatively unaffected by thermal characteristics or process corner inconsistency.

In the past, Renesas used dedicated multi-port memory cells while at the same time developing SRAM for highly accurate and faster video data processing. But that approach presented challenges with increased on-chip area and power leakage because more elements were required than with ordinary single-port memory cells. Renesas developed an SRAM macro using conventional single-port SRAM cells that implements the double-pumping circuit technology to enable simultaneous read and write operations in a single clock cycle.

Renesas recently presented the aspects of its new SRAM technology, including both the double pumping and low circuit design using FinFET, at the 2016 Symposia on VLSI Technology and Circuits. Nii sees a lot of potential in the automotive market to support ADAS and other infotainment systems with more complex graphics including 3D, as well as the autonomous vehicle segment.

SRAM is not the only memory that is finding its way into vehicles, of course. It all depends on the application. For example, when Cypress acquired Spansion, it also inherited that company's HyperRAM technology, an alternative to the commonly used options of SRAM or PSRAM. Its fast read time makes it suitable for automotive applications such as such as instrument clusters, infotainment and advanced driver assistance systems.

Flash and DRAM also have a role to play in automotive systems. Last year, Micron debuted its XTRMFlash memory, specifically for applications that have an “instant on" requirement. The low pin count NOR flash memory supports human-machine interface with graphical user display, instrument clusters, infotainment systems and advanced driver assistance systems (ADAS).

Micron's

XTRMFlash memory is designed for applications that have an “instant on"

requirement, including instrument clusters, infotainment systems and

advanced driver assistance systems (ADAS).

Meanwhile, FRAM is also a candidate for automotive, as it can be used for nonvolatile data logging in most automotive sub systems such as smart airbags, stability control, power train, dashboard instrumentation, battery management, engine controls and infotainment applications. AEC-Q100 qualified FRAMs are built to bear the extended grade temperatures under the hood.

Research firm Databeans predicts the automotive semiconductor market will reach a high of $40 billion in 2020, thanks to the growing amount of electronic content in today's vehicles such as assisted-driving systems, built-in GPS, satellite radio menus, vehicle-to-vehicle communications and other infotainment systems.

http://www.eetimes.com/document.asp?doc_id=1329958

No comments:

Post a Comment