PORTLAND, Ore. — The future of

three-dimensional (3D) very large scale integration (VLSI) for

system-on-chips (SoCs) will not stack die connected by

through-silicon-vias (TSVs), but will build them on a single layered

die, according to Karim Arabi, vice president of engineering at Qualcomm

speaking at the International Symposium on Physical Design (ISPD-2015,

Mar. 29-April 1).

"Our 3D VLSI technology, which we call 3DV, enables die size to

be shrunk in half, while simultaneously increasing yields," Arabi told

us.Qualcomm's motivation, according to Arabi, is market share in the 18 billion smartphones that he predicts will be produced by 2018 — "more than all the computers and other electronic devices combined," he told us. He also noted that even though the cloud is offloading some computationally intensive applications — such as speech recognition — there will still be an increasing need for local processing power for most smartphone functions.

Karim

Arabi, vice president of engineering at Qualcomm describes how its

next-generation SoCs will use up to three layers without

through-silicon-vias (TSVs) to reduce die size and increase yields.

(Source: EETimes)

(Source: EETimes)

Qualcomm is creating two basic types of 3DV interconnection methods with the hope of deploying them by 2016. These new types of 3D interconnection comes in two flavors face-to-back (F2B) and face-to-face (F2F).

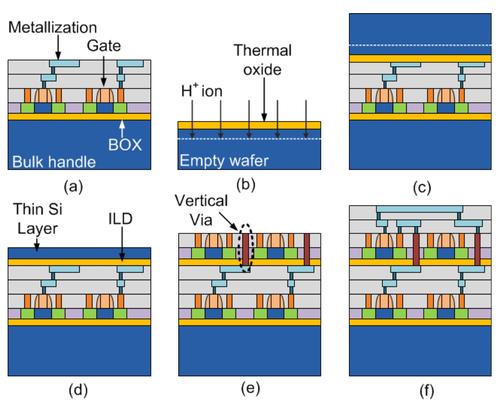

In the

fabrication process of front-to-back (F2B) 3DVs (a) the bottom tier is

created the same way as 2D-ICs. (b,c,d) To add another layer, first a

thin layer of silicon is deposited on top of the bottom tier. (e) This

front-end-of-line (FEOL) process of the top tier permits the addition of

normal vertical vias and top-tier contacts. (f) Finally

back-end-of-line (BEOL) processing creates the top-tier.

(Source:Qualcomm)

(Source:Qualcomm)

F2F, on the other hand, allows both chips to use copper interconnects and optimally performing transistors, but has the disadvantage, according to Arabi, that the F2F method requires larger vias the size of which are limited by the accuracy with which the two facing wafers can be bonded. Qualcomm, however, believes that by using a mix of the two techniques it will be able to produce fully optimized 3DV SoCs with an unlimited number of layers. In fact, with appropriate partitioning and floor planning, Arabi believes 3DV chips can be produced that are faster, smaller, consume less power and operate at lower temperatures than putting the same functions on a single 2-D chip.

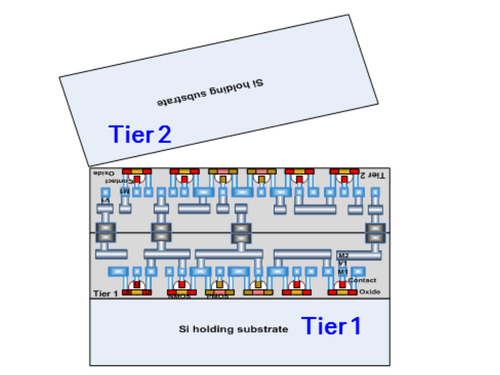

In the

fabrication process of front-to-front (FF) 3DVs requires wafer-level

bonding and hence the vias can only be a small as the accuracy of the

bonding method.

(Source: Qualcomm)

(Source: Qualcomm)

http://www.eetimes.com/document.asp?doc_id=1326174

No comments:

Post a Comment